FPGA因其高吞吐性能和硬件可编程特性,是数据中心、广域网和云计算场景下关键的网络加速引擎之一。然而,目前FPGA网络加速引擎在业界存在2个难题: 1)即使FPGA硬件还有多余硬件资源,上层多个APP软件难以虚拟化共享同一片FPGA硬件资源; 2)当网络功能变化时,FPGA网络匹配表的深度和宽度无法快速适应变化,而重新设计和编译FPGA需要花费大量的时间。

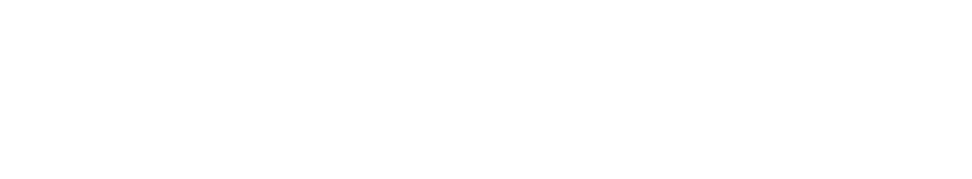

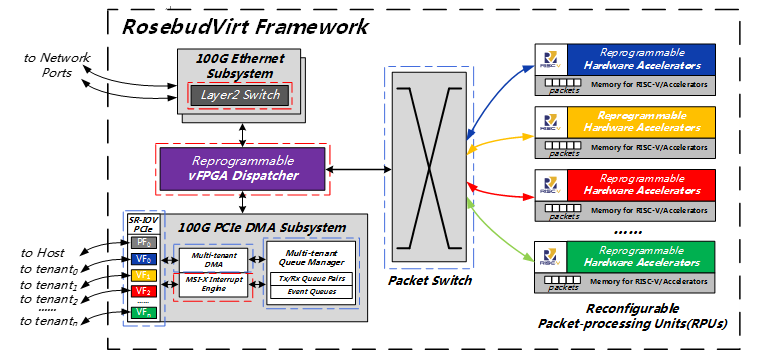

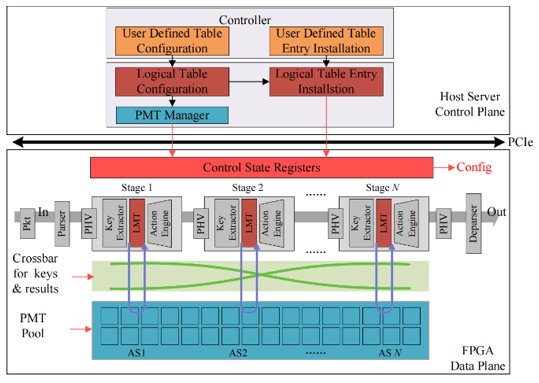

为此,中国科学院声学研究所智能网络与信息处理技术实验室博士生常艺伟、宋晓勇及其导师郭志川研究员提出了一种用于多应用高性能部分可重构FPGA虚拟化框架——RosebudVirt,可将同一片FPGA划分为多个分片,每个分片互相独立,并用一个容器Docker进行管理,基于Docker可为多个APP应用提供可自定义的网络加速服务,并基于K8S进行容器集群管理,该方法还为统一管理异构硬件资源提供了解决方案; 此外,针对FPGA网络匹配表的动态可重构问题,他们还提出了基于FPGA的动态可配置流表的方法,通过寄存器配置,可实现快速更改匹配表的数量、宽度和深度,很大程度上方便了新的网络功能在FPGA数据平面中的快速部署。

相关研究成果连续2篇在线发表于大规模集成电路领域国际学术期刊 IEEE Transactions on Very Large Scale Integration Systems上。

本研究得到中国科学院战略性先导科技专项课题:信息协同服务数据共享技术研究(No.XDA031050100)和国家重点研发计划:软件定义互连芯片与配套软件开发(No.2022YFB2901004)资助。

图1 RosebudVirt框架示意图(图/中国科学院声学研究所)

图2 RosebudVirt收发吞吐(图/中国科学院声学研究所)

图3 可配置匹配表及验证系统架构图(图/中国科学院声学研究所)

关键词:FPGA虚拟化;多租户;部分可重构;容器;可重构匹配表;掩码匹配表;精确匹配表

参考文献:Yiwei Chang and Zhichuan Guo. RosebudVirt: A High-Performance and Partially Reconfigurable FPGA Virtualization Framework for Multitenant Networks. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2024. DOI: 10.1109/TVLSI.2024.3436017

参考文献:Xiaoyong Song and Zhichuan Guo. An Implementation of Reconfigurable Match Table for FPGA-Based Programmable Switches. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2024. DOI:10.1109/TVLSI.2024.3436047